### Application Note

AN2467/D Rev. 0, 03/2003

Power Quad Flat Pack No-Lead (PQFN)

| Торіс                                                                                 | Page                     |

|---------------------------------------------------------------------------------------|--------------------------|

| 1.0 Purpose                                                                           | 1                        |

| 2.0 Scope                                                                             | 1                        |

| 3.0 Power Quad Flat No-<br>Package                                                    | -lead (PQFN)<br>1        |

| 3.1 Package Descripti                                                                 | on1                      |

| 3.1.1 Package Appl<br>3.1.2 Package Dime<br>3.1.3 PQFN Package<br>3.2 PQFN Assembly F | ensioning2<br>je Design2 |

| 4.0 Printed Circuit Board                                                             | Guidelines 3             |

| 4.1 Printed Circuit Boa<br>PQFN Packages                                              | ard Design for           |

| 4.2 Solder Paste Sten<br>PQFN Packages                                                | cil Design for           |

| 5.0 2nd Level Reliability<br>Experimental Solder Jo                                   |                          |

| 6.0 Theoretical Solder-Jo<br>Modeling Results                                         | oint Reliability         |

| 7.0 Thermal Performanc<br>Results                                                     | e Modeling               |

| 8.0 APPENDIX                                                                          | 13                       |

8.1 Case Outline Drawings ......13

## 1.0 Purpose

This document provides guidelines for Printed Circuit Board (PCB) design and assembly. Package performance attributes such as Moisture Sensitivity Level (MSL) rating, board level reliability and thermal resistance data are included as reference.

intelligence everywhere"

## 2.0 Scope

This document is written to generically encompass several different Power Quad Flat No-lead (PQFN) packages assembled at Motorola internal assembly sites and external subcontractor sites. It should be noted that device specific information is not provided. This document serves only as a guideline to help develop a user specific solution. Development effort will still be required by end users to optimize PCB mounting processes and board design in order to meet individual-specific requirements.

# 3.0 Power Quad Flat No-lead (PQFN) Package

## 3.1 Package Description

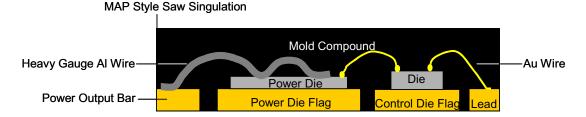

The PQFN is a surface mount plastic package with lead pads located on the bottom surface of the package. All PQFN packages have either been designed with a single exposed die pad (flag) or multiple exposed die pads depending on device requirements and intended application. The industry standardization committee, JEDEC, will have design guidelines and structure descriptions for these package types when established. This JEDEC registration is in-progress for several PQFN designs.

## 3.1.1 Package Application

The PQFN surface mount packages have been designed to meet the high power dissipation requirements of automotive, industrial, and commercial applications. Features such as solder die attach material, thick copper lead frames, exposed heat sinks, and heavy gauge aluminum wire capability allows for efficient heat transfer out of the PQFN packages.

### Power Quad Flat No-lead (PQFN) Package

## 3.1.2 Package Dimensioning

Currently, there are PQFN packages ranging from 10 x 10 mm to 12 x 12 mm in body size. Lead counts range from 16 to 35 at this time. The lead pads have been designed in both single-row and double-row configurations depending upon the specific package requirements. The lead pitch of the perimeter leads is either 0.8 or 0.9 mm.

## 3.1.3 PQFN Package Design

While there are many different package configurations available, the PQFN package platform differs from the standard QFN package platform (JEDEC: M0-220) by having the following characteristics in Table 1.

| Characteristic      | QFN (JEDEC: MO-220)          | PQFN                              |

|---------------------|------------------------------|-----------------------------------|

| Lead Pitch          | 0.65 mm or less              | 0.8 mm or more                    |

| Leadframe Thickness | 0.13 - 0.20mm (5 - 8 mil) Cu | 0.51mm (20 mil) Cu                |

| Package Thickness   | 1.0mm or less                | 2.1 mm                            |

| Die Attach          | Epoxy Only                   | Epoxy and/or Solder               |

| Wire Bonding        | (1.0 mil – 2.0 mil) Au Wire  | Small gauge Au and large gauge Al |

| Exposed Flags       | 1 Flag                       | 1 or more flags                   |

Table 1. Differences Between QFN and PQFN Packages

Singulation is similar to that of the original QFN package.

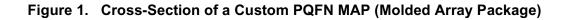

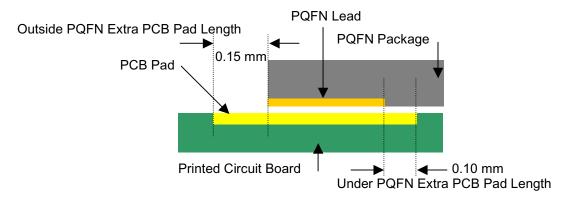

# 3.2 PQFN Assembly Process Flow

Figure 2 displays the PQFN assembly process flow steps referred to as Mold Array Packaging (MAP). The MAP process steps are very similar to the QFN process steps except for the addition of solder paste die attach, de-flux with de-ionized water rinse and taping process steps. The wire bond process may include both Au wire ball-bonding as well as AI wire wedge-bonding, depending on the application requirements. The molded array is singulated with a saw scribing process that leaves vertical edges on the body of the PQFN packages.

Figure 2. Mold Array Packaging Process Flow for the PQFN Package

# 4.0 Printed Circuit Board Guidelines

## 4.1 Printed Circuit Board Design for PQFN Packages

PQFN packages have unique and varied footprints due to the use of exposed pads for thermal management. Care should be taken to design pads on a PCB that are compatible with the arrangement of unique features on the bottom side of PQFN packages. The following guidelines can be used to help address a user specific solution.

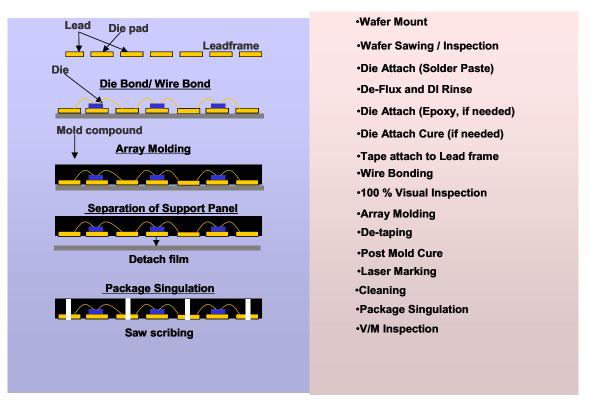

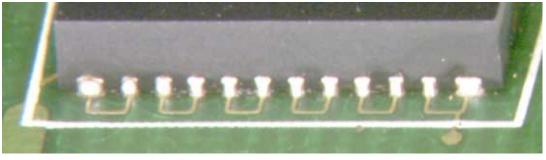

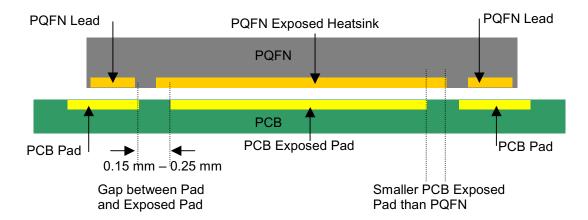

The board design should begin with copper pads that sit beneath the periphery leads of a mounted PQFN. These board pads should extend outside the PQFN edge a distance of approximately 0.15mm. See Figure 3. The extra solder that will form outside the package edge will create a useful, yet imperfect, visual indication of solder joining the package after reflow processing, as shown in Figure 4. The copper board pads should also extend beneath the package approximately 0.10mm beyond the inner lead edge, as shown in Figure 3.

Figure 3. A Cross-Section of Package Lead and Suggested PCB Pad

Figure 4. Example of Visible Solder-Joint Exterior to a PQFN Package

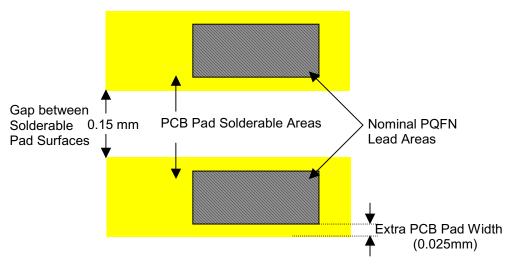

The pad width should be approximately 0.025mm wider than the nominal lead dimension on each side. See Figure 5. Increasing the pad width 0.025mm on both sides (0.05mm total) helps with placement of parts during assembly by allowing a larger target for the PQFN to be seated. It will be important to keep at least 0.15mm board spacing between adjacent pads. The 0.15mm spacing will keep solder from bridging between neighboring leads, thereby electrically shorting them together.

Figure 5. Top View of PCB and Suggested PCB Pad Size for PQFN Leads

After completion of the periphery pad design, the larger exposed pads will be designed to create the mounting surface of the PQFN exposed heat sink(s). The primary transfer of heat out of the PQFN will be directly out the bottom surface of the exposed heat sink(s). It is recommended to use an array of plated through-hole vias beneath the mounted part to aid in the transfer of generated heat into the PCB. The specific diameter and pitch of the via hole array will need to be defined by the end user are typically consistent in size with other drill hole diameters found on the application PCB. The JEDEC committee proposes an array of plated vias for thermally standardized testing with via hole diameters of 0.3mm with a center-to-center pitch of 1.2mm per JESD51-5. This via pattern can be used as a starting point for creating a customer specific board design.

A PCB exposed pad that is lined with periphery pads, having at least 0.15 mm spacing between the pad edge and the exposed pad, would again provide some assurance against solder bridging. Since there can be a large volume of solder needed beneath the package, to cover the large exposed pad region, the 0.15mm spacing can be increased to approximately 0.25mm. See Figure 6. There will often be a resulting PCB exposed pad that is smaller in size than the PQFN exposed heat sink(s) after the application of the noted guidelines. See Figure 6. It is okay if this situation exists since there will likely be a sufficient volume of solder beneath the PQFN exposed heat sink to mount the package.

Figure 6. Example of Spacing Between PCB Pad and Exposed Pad

# 4.2 Solder Paste Stencil Design for PQFN Packages

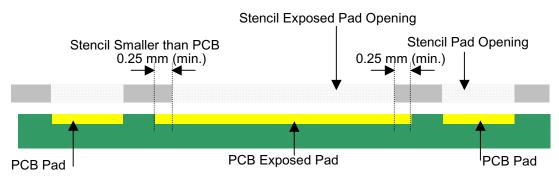

In general, solder paste stencil aperture openings can be on-to-one (1:1) with the peripheral PCB pad sizes. However, the stencil aperture openings should be smaller than the large PCB exposed pad regions to reduce the chance of solder bridging. There will be a larger volume of solder in the PCB exposed pad region so it is necessary to create additional physical space between the exposed pad and the surrounding PCB pads. It is suggested to reduce the stencil aperture opening by a minimum of 0.25mm as seen in Figure 7.

Figure 7. Reduced Solder Stencil Aperture for Exterior of Exposed Pad

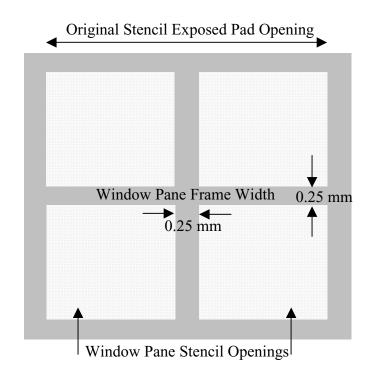

During the solder screen print operation, a stencil blade can both deposit solder paste and remove, or "scoop" it in large aperture openings. In the large openings, the blade bends down into the opening thereby leaving less solder volume than anticipated. To mitigate the effect of scooping, the aperture can be broken up into an array of smaller openings. The array of openings will resemble a "window pane" pattern as seen in Figure 8. Large PCB exposed pads that are approximately 3.2mm x 3.2mm or larger in size should have a "window pane" stencil opening pattern. It is suggested that a spacing of 0.25mm is used between the individual panes. See Figure 8. This recommendation must be confirmed by solder reflow processing followed by X-ray analysis. Any voiding in the reflowed solder should be minimized. It is possible to get incomplete wetting between the PQFN and the PCB exposed pad. Incomplete wetting can occur if the "window pane" pattern is not properly optimized with the reflow wetting process.

Stencil thickness can play an important role in solder joining. The stencil thickness is usually chosen by a combination of both typical industry practices and the requirements of the other components on a PCB module. Motorola has had success with solder joining processing by using stencil thickness of both 0.125mm and 0.150mm (5 and 6 mils). If stencils with a thickness greater than 0.150mm are used, it is suggested to investigate a reduction of the stencil opening size, thereby reducing total solder volume to minimize the risk of solder bridging. For stencils thinner than 0.125mm, aperture openings may have to be increased in order to provide enough volume of solder to get complete solder wetting between all contact surfaces.

Figure 8. Window Pane Pattern for Exposed Pad Stencil Opening

# 5.0 2<sup>nd</sup> Level Reliability Data: Experimental Solder Joint Analysis

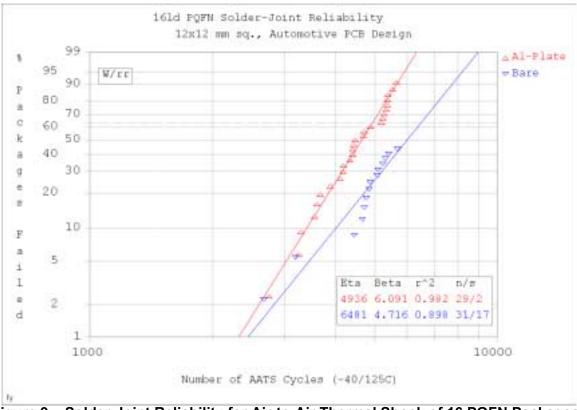

Several 16 PQFN packages (Fig 8.1) were mounted using a eutectic (Sn<sub>37</sub>Pb<sub>63</sub>) solder, to a 2-layer PCB that is considered typical of many automotive and industrial application designs. The PCB had a total thickness of 0.65mm with 70um thick copper layer on both top and bottom surfaces. Half of the test boards were mounted to thick Aluminum plates with an industry common adhesive tape. The attached plates simulated the mechanical forces found in typical automotive electronic modules that are mounted within an aluminum housing. The test boards with mounted PQFN packages were placed into temperature chambers for cycling. A package "failure" was recorded when any single solder joint failure occurred. The data in Figure 9 was generated by air-to-air thermal shock (AATS) cycling between –40°C and 125°C. One cycle consisted of 15 minutes at each temperature extreme and a very short transfer time between chambers. Air-to-air thermal shock is an accelerated solder joint reliability test that Motorola uses to quickly determine reliability in an application design. Gathered AATS data is to be compared with air-to-air temperature cycling (AATC) data to find correlation that will allow predictive analysis of reliability in a shorter time period. The Weibull plots shown in Figure 9 and Figure 10 can be used to determine the predicted first time to failure (FTTF) based upon a correlation plot of measured failures. The predicted FTTF is estimated to be the number of cycles measured when the linear correlation line crosses the horizontal axis.

#### 2nd Level Reliability Data: Experimental Solder Joint Analysis

Figure 9. Solder-Joint Reliability for Air-to-Air Thermal Shock of 16 PQFN Packages

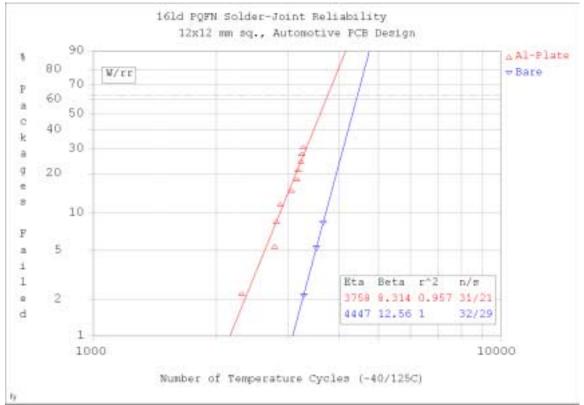

At the time of this writing, the AATC study had accumulated 3743 cycles of -40°C and 125°C cycling. The AATC study will remain in progress until 75% failure is achieved. One cycle of AATC consists of a 1-hour duration with a 15-minute dwell at temperature and 15-minute ramps between temperature extremes. The first recorded failure for the aluminum plated PCB boards occurred at 2308 cycles with 9 more failures to date. See Figure 10. The bare PCB board group, with less mechanically induced forces, had the first failure reported at 3280 cycles with 2 more additional failures to date. The results of the AATC reliability data are plotted in Figure 10. Motorola will complete this set of experiments and provide updates that can be obtained through Motorola sales offices and/or updates application notes. As more PQFN packages are designed, Motorola will continue to more gather solder joint reliability data as needed.

Figure 10. Solder Joint Reliability for Air-to-Air Temperature Cycling of 16 PQFN Packages

The solder joint reliability data in Figure 9 and Figure 10 should be considered achievable under similar mounting and testing conditions. Customer specific board designs and temperature cycling ranges will vary results. End users are encouraged to conduct their own solder joint reliability experiments.

# 6.0 Theoretical Solder-Joint Reliability Modeling Results

Motorola has conducted finite element model simulations of the creep and strain that PQFN solder-joints would experience during temperature cycling. Results indicate that the solder-joints with highest strain rates are those at the corner of the package. These solder joints have the most strain at the pad backside under the package and not at the fillet solder located on the exterior bottom edge of the packages. The large exposed pads of the PQFN see little to no strain during temperature cycling. Motorola will continue to refine the simulation as more experimental data becomes available and as more devices are packaged into PQFN type packages.

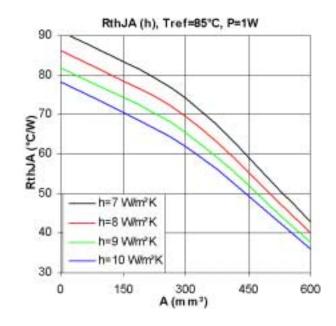

# 7.0 Thermal Performance Modeling Results

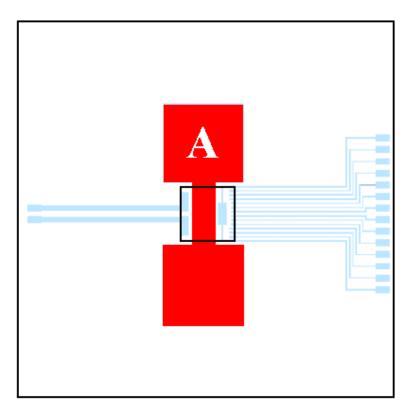

The 16 PQFN package has been modeled to obtain thermal performance values. Figure 11 shows a top-view of the single-layer printed circuit board measuring 80mm x 80mm x 1.6mm used in the thermal model. A 35um thick copper top-layer formed the lead traces and also a heat spreader area, represented by "A". The heat spreader area was used to remove heat from the bottom surface of the PQFN and spread it onto the PCB. A copper strip that was 0.3mm in width was modeled directly beneath the PQFN and in contact with an exposed heat sink.

MOTOROLA

Figure 11. Thermal Model of a MC33982FC in a 16 PQFN Package Mounted to a Single-Layer PCB

The board used in the modeling produced conservative results considering it is a single-layer PCB that has a layer of copper on the top surface only. A more efficient board design would include a multi-layer board with plated through-hole vias beneath the mounted part. The heat could then transfer through the board and spread to the connected Cu layers or possibly to a larger heat sink such as a metal module housing. The model was performed with various sizes of heat spreader areas, labeled "A", to represent the effect of improving dissipation onto the PCB. Table 2 is a summary of resulting thermal resistance values obtained for a range of convection coefficients (h). The convection coefficient will range from approximately 5W/mK to 10W/mK for natural convection (still air) applications in a broad array of mounting conditions. Mounting conditions could include vertical or horizontal mounting in open air or inside a closed container such as a module housing. The thermal resistances from the die junction to the ambient, case, and lead pad are reported.

|       |                     | h (W/m²K) |      |      |      |  |

|-------|---------------------|-----------|------|------|------|--|

|       | A (mm) <sup>2</sup> | 7         | 8    | 9    | 10   |  |

| RthJA | 0                   | 91        | 86.2 | 81.9 | 78.2 |  |

| °C/W  | 300                 | 74.3      | 69.4 | 65.4 | 62   |  |

|       | 600                 | 43        | 40.1 | 37.7 | 36   |  |

| RthJC | 0                   | 0.9       | 0.8  | 0.9  | 0.8  |  |

| °C/W  | 300                 | 0.8       | 0.8  | 0.8  | 0.9  |  |

|       | 600                 | 0.5       | 0.6  | 0.6  | 0.9  |  |

| RthJB | 0                   | 29.4      | 29.2 | 28.9 | 27.8 |  |

| °C/W  | 300                 | 22.4      | 22.1 | 21.8 | 21.1 |  |

|       | 600                 | 12.9      | 12.8 | 12.7 | 11.8 |  |

### Table 2. Steady State Analysis Summary of MC33982FC in a 16 PQFN Package

Note: RthJA = Thermal Resistance Junction-to-Ambient

RthJC = Thermal Resistance Junction-to-Case

RthJB = Thermal Resistance Junction-to-Lead

As the heat spreader area "A" is increased, the thermal resistance from junction to ambient will be reduced. This occurs because the junction temperature will be reduced when the generated heat can be transferred away from the package more effectively as seen in Figure 12. In an actual application, heat transfer can be improved through Cu heat spreader planes on both top and bottom surfaces to two-layer boards. Internal Cu planes can also be used to spread heat in multi-layer PCB applications.

Figure 12. RthJA (Junction-to-Ambient) Resistance Versus Heat Spreader Area

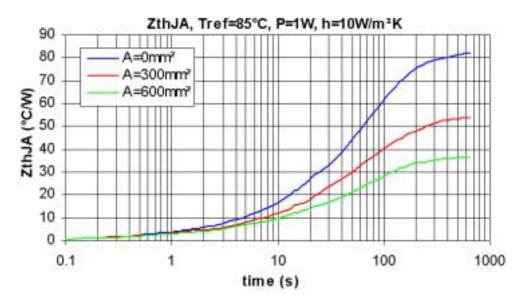

In a steady state condition, Figure 12 shows that the heat spreader area can greatly affect the thermal resistance for the same mounting conditions. The benefit of thermal heat spreading in a PCB for transient conditions can also be seen in Figure 13. Figure 13 shows detail of the initial transient response curve for 1Watt

MOTOROLA

#### **Thermal Performance Modeling Results**

power dissipation at a relatively high convection coefficient condition (h=10W/m<sup>2</sup>K). The transient thermal resistance is inversely related to the amount of heat spreader area is provided.

Figure 13. Transient Analysis of ZthJA for MC33982FC in a 16 PQFN Package

Figure 13 represents the full transient response of the junction-to-ambient thermal resistance, RthJA, until steady state response is reached near 600 seconds. The boundary conditions modeled between Figure 12 and Figure 13 remain the same for comparison.

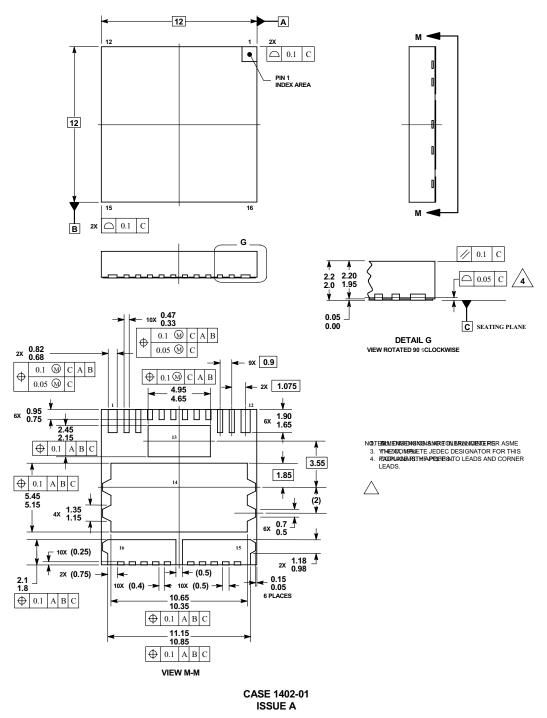

# 8.0 APPENDIX

## 8.1 Case Outline Drawings

DATE 04/30/02

### Figure A-1. 16 Lead PQFN, Case No. 1402

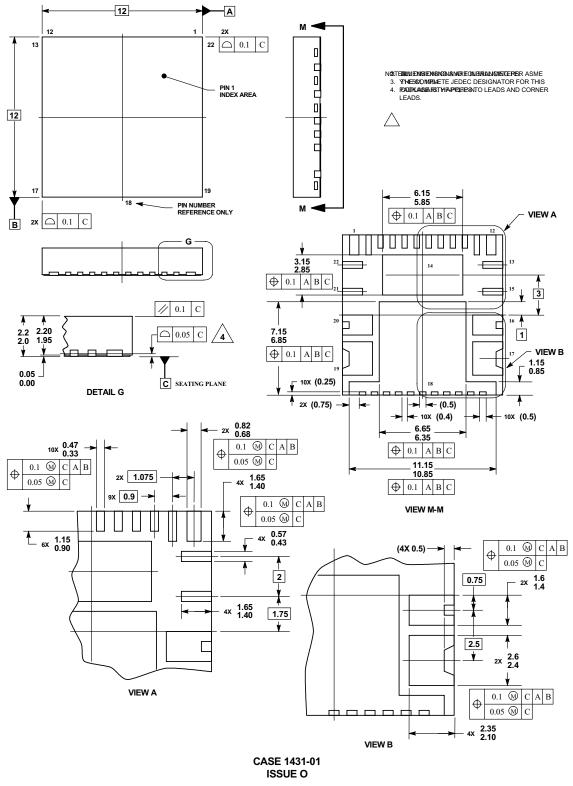

DATE 05/03/02

Figure A-2. 22 Lead PQFN, Case No. 1431

Power Quad Flat Pack No-Lead (PQFN) Preliminary Copy - Unreleased

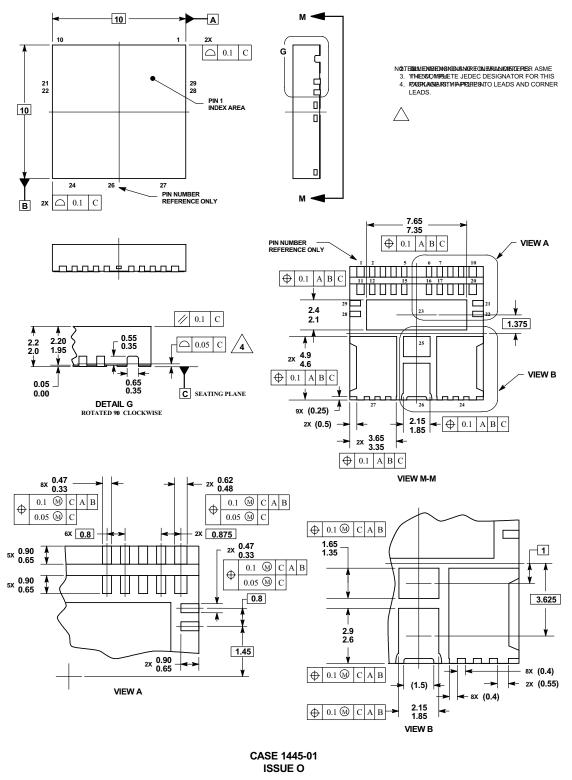

DATE 07/18/02

Figure A-3. 29 Lead PQFN, Case No. 1445

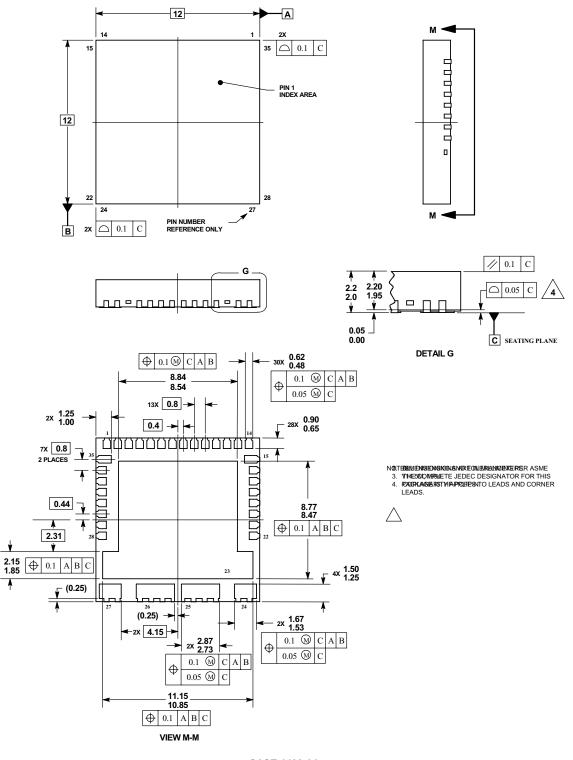

CASE 1438-01 ISSUE O

DATE 08/02/02

### Figure A-4. 35 Lead PQFN, Case No. 1438

THIS PAGE INTENTIONALLY LEFT BLANK

THIS PAGE INTENTIONALLY LEFT BLANK

THIS PAGE INTENTIONALLY LEFT BLANK

#### HOW TO REACH US:

#### USA/EUROPE/LOCATIONS NOT LISTED:

Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-441-2447 or 480-768-2130

#### JAPAN:

Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1, Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd. Silicon Harbour Centre, 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T. Hong Kong 852-26668334

#### HOME PAGE:

http://motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners. © Motorola Inc. 2003

AN2467/D Rev. 0 03/2003